PXSu – USB to Synchronous Adaptor

What is it?

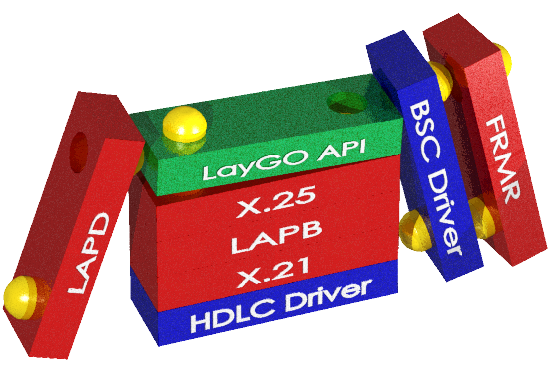

The PXSu is a USB to synchronous adaptor. Connected directly to a computer’s USB port or indirectly through a USB hub, the PXSu can provide synchronous communication just as an internal synchronous adapter does. Combined with low cost notebooks or PCs and their peripheral devices, the PXSu can support a wealth of new applications, such as synchronous to TCP/IP or wireless. Synchronous protocols, such as LAPB, LAPD, X.25, Bisynchronous and Monosynchronous are supported through our LayGO® multiprotocol host services.

USB, the Alternative for PCMCIA and PCI

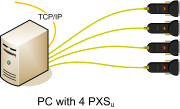

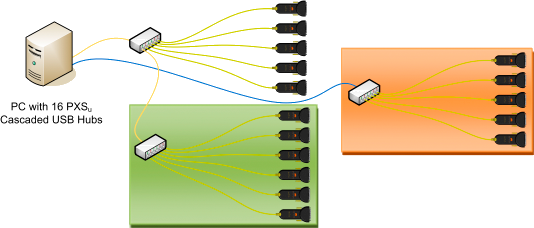

Nearly all PCs or computers today come with built-in USB and Ethernet ports, supported by the operating systems. Because of the wide use of USB, the PXSu is a true alternative for disappeared synchronous PCMCIA and PCI adaptors. No notebook today supports PCMCIA cards. Current notebooks come at least with 2, PCs with 4 USB ports or more. Each USB port can be converted by the PXSu to a synchronous port supporting HDLC protocols such as X.25, LAPB or others. If required, USB hubs can increase the number of synchronous lines available.

Synchronous Port

The synchronous port uses a built-in DB25 connector, configurable for RS-232, RS-422, RS-485 and V.35. RS-232 supports 128 kbps; RS-422/485 and V.35 support 4.096 Mbps (2xE1) (Self encoding clock modes support up to 512 Kbps). If the PXSu operates as DCE (clock source), the DB25 connector is X-Over female; as DTE (clock sink), straight male.

The PXSu supports bit synchronous and byte synchronous modes. Bit synchronous can be bit-transparent or HDLC/SDLC; byte synchronous can be Bisynchronous or Monosynchronous. Data encoding can be NRZ, NRZI, FM0, FM1 or Manchester. Each PXSu can be independently configured: DTE or DCE, RS-232, RS-422 or V.35, HDLC or Bisynchronous, X.25/LAPB or X.25/LAPD, etc.

The PXSu as a Synchronous Apdaptor

The PXSu operates exactly as an internal synchronous adaptor. Current users of PCI, PCMCIA, PC/104, PMC and even ISA cards need only replace the existing LayGO® API DLL. No changes to existing LayGO® applications are necessary.

What does it include?

In addition to the PXSu synchronous adaptor, we provide LayGO®, our highly modular multiprotocol stack (X.25, LAPB, LAPD, NRM, Frame Relay and proprietary). The combined use of LayGO and host-based TCP/IP or wireless services provides a great variety of communication solutions. Besides HDLC, we support drivers for SDLC, bit transparent, Bisynchronous and Monosynchronous modes.

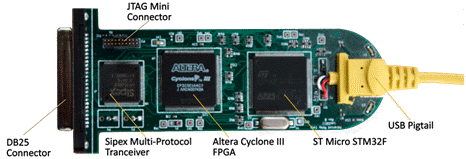

Hardware

The PXSu is very compact, with built-in DB25 connector (male or female) and a USB pig-tail. DB25 is the most common connector, used by RS-232, EIA-530 and often by V.35. Normally, the male connector uses thumbscrews, the female hex nuts. If other connectors are required, such as Winchester for V.35, DB15 for X.21 or DB37 for RS-449 (V.36), adaptor cables can be provided. Two programmable LEDs (1 green, 1 red), and 3 states of operation (off, on, blinking) indicate the state of operation of the PXSu.

A powerful feature of the PXSu is support for the USB DFU specification, which allows field updates of the firmware and the FPGA net map.

The major PXSu>components are a microprocessor, an FPGA and a programmable I/O chip:

- STMicroelectronics STM32F 32-bit Cortex M3 ARM7 microprocessor, 64 KB SRAM and 512 KB with XIP (eXecute In Place) NOR-Flash, built-in USB device controller

- Altera Cyclone III EP3C5 FPGA, with 5,136 Logic Elements and 414 Kbits RAM

- SIPEX SPC3508 Multiprotocol Transceiver asynchronous/synchronous serialport(s)

FPGA

One of the most powerful features is provided by the FPGA (Field Programmable Gate Array). Because of sketchy synchronous communication support by microprocessors, Advanced Relay developed a class of efficient LayGO/Sync cores using VHDL. The HDLC core uses only 16% of the FPGA’s 5,136 logic elements and includes the configuration of the board ID, asynchronous or synchronous port selection, DTE/DCE clock routing and RS-232, RS-422, V.35 signaling mode. The remaining capacity can be used to design custom features in VHDL, such as 13-bit bound Radar Protocols, data encryption, data compression, USB-core, wireless protocols, etc.

[Last updated February 21st, 2024]